Image Credits: GizmoChina

Taiwan Semiconductor Manufacturing Company (TSMC) has revealed that chips created on the 3nm production method would be available in 2023, and those made on the 2nm technology will be available in 2025.

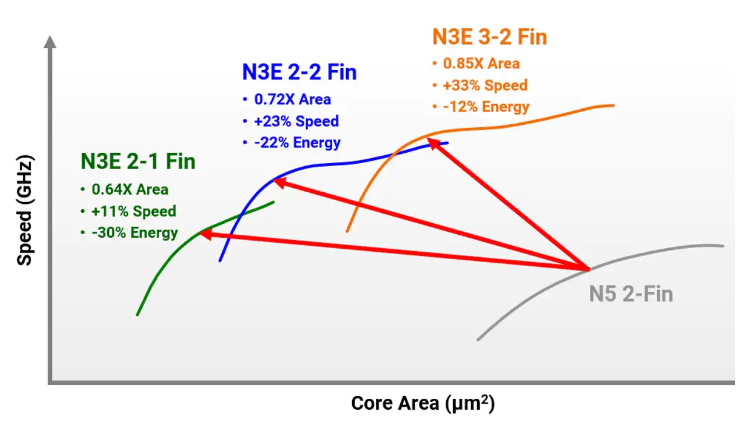

The chipmaker also introduced a new technology, FinFlex, that it would employ to create the N3 and N3E chipsets at the TSMC 2022 Technology Symposium. Based on three-fin arrangement possibilities, the technology is supposed to give manufacturers the flexibility to deliver excellent performance, low power consumption, and maximum transistor density.

TSMC 3NM Chipset launch by 2023

According to the statement made at the symposium, N3 technology chipsets, or 3nm manufacturing processes, will enter volume production later in 2022. The 3nm node will be available in five different configurations: N3, N3E (Enhanced), N3P (Performance Enhanced), N3S (Density Enhanced), and N3X. (Ultra High Performance). The N3 chips will employ FinFlex architectural technology and will be available in three configurations: 3-2 fin, 2-2 fin, and 2-1 fin.

Image Credits: Gadgets NDTV

“Before TSMC N3 and FinFlex, chip designers frequently would have to choose between speed, energy consumption, as well as chip compact,” the firm explained. According to with company, the new technique would “allow comprehensive optimization of the N3 design library,” resulting in an excellent performance, efficient processing, and maximum transistor density.

The 3-2 fin layout is designed for maximum performance, while the 2-2 fin configuration strikes a compromise between performance, power efficiency, and density. Finally, the 2-1 fin arrangement is ideal for individuals seeking maximum power efficiency and density.

TSMC 2NM Chipset Production to begin by 2025

In terms of N2 technology, chipsets built using the 2nm manufacturing process are expected to enter production in 2025. These SoCs will be even faster and more efficient than the 3nm ones.

According to TSMC, 2nm chips will give a 10-15% speed gain at the same power, or a 25-30% power reduction at the same speed. The nanosheet transistor design will be used in the technology to “provide a full-node increase in performance and power efficiency.” N2 is set to go into production in 2025.

The North America Symposium in Santa Clara, California, resumes as an in-person event after being hosted online for the previous two years and starts off a series of Technology Symposiums throughout the world in the following months. The Symposiums also include an Innovation Zone, which showcases the accomplishments of TSMC’s emerging start-up clients.